뭘 알아야 이해를 하지

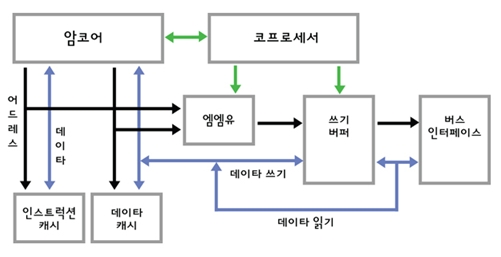

시피유 내에는 암코어, 코프로세서, 엠엠유, 캐시메모리 기타 등등이 있지요. 여기서 코프로세서가 하는 역할은 엠엠유 ON/OFF, 캐시 메모리 ON/OFF등을 한답니다. 코프로세서는 CP15라고 불려지기도 하죠. 그림과 같이 인스트럭션 캐시와 데이터 캐시에 어드레스와 데이터 선이 따로 연결되어 있는 것을 하바드(Harvard) 설계 방식이라고 합니다. 주로 암9 이상부터 많이 사용하는 방식이랍니다. 이렇게 인스트럭션 캐시와 데이터 캐시에 어드레스와 주소가 따로 있다는 것은 인스트럭션 캐시에 명령어를 읽을 때 데이터 캐시에 쓸 수가 있어서 성능이 매우 우수하죠.

암코어와 코프로세서간에는 어셈블리 명령에 의해서 서로를 동작시킬 수가 있으며, 주로 코프로세서 어셈명령어로 엠엠유나 캐시 메모리를 동작하게 된답니다. 여기서 암코어는 37개의 레지스터가 있으며 코프로세서도 15개 내외로 레지스터가 있어요. 하드웨어 디버거로 레지스터를 자세히 들어다 본다면, 아래와 같아요.

<암 코어 레지스터>

N N R0 6F24 R8 0

Z _ R1 0 R9 0

C _ R2 7 R10 0

V _ R3 36 R11 0

I I R4 R12 25

F F R5 56CC R13 0FE4

T _ R6 0 R14 6

R7 0 PC 22D0

svc SPSR 10 CPSR 800000D3

<코프로세서 레지스터>

CR 00000000 iA 0 nF 0 RR Random V 0x00000000

I Disable R Disable S Disable B Little

C Disable A Disable M Disable

TTBR 00000000 TTBA 00000000

DACR 00000000 D15 Denied D14 Denied D13 Denied D12 Denied

D11 Denied D10 Denied D9 Denied D8 Denied

D7 Denied D6 Denied D5 Denied D4 Denied

D3 Denied D2 Denied D1 Denied D0 Denied

코프로세서 레지스터를 자세히 보시면 CR, TTBR, DACR 과 같이 15개 내외의 레지스터가 있는데, CR레지스터를 분석해 보면 가장 중요한 비트인 I, C, M 가 있네요. 이 비트들의 의미는 I:인스트럭션 캐시(Instruction Cache), C:데이타 캐시(Data Cache), M:엠엠유(MMU) 랍니다. 즉, CR레지스터를 조절하면 I-Cache, D-Cache, MMU를 on/off를 할 수 있죠.

CR레지스터에서 M비트만 ON이 되면 "200 유닛" 에서 말씀 드린 엠엠유 역할을 하게 되죠. 여기서 중요한 사실 한가지를 알아 본다면 캐시 메모리는 M비트가 반드시 ON이 되어야지 캐시 메모리를 사용할 수가 있어요. 그림을 자세히 보시면 I-Cache, D-Cache 어드레스가 모두 엠엠유로 연결되어 있기 때문이죠.

그럼 CR레지스터에서 M비트가 On이 된다는 것은 소프트웨어적으로 어떻게 이해를 해야 할까요? 가상주소가 만들어 진다고 하는데 어떤 의미일까요?

엠엠유 OFF 상태일 때는 시피유가 에스디램 어드레스를 접근을 하지만 엠엠유 ON일 때는 가상주소로 접근을 한답니다. 가상의 주소는 실제로 에스디램처럼 물리적인 메모리가 있는 것이 아니라 단지 어드레스만 제공하고 실제 데이타는 에스디램에 있답니다.

여기서 시피유가 가상주소로 접근을 하면 에스디램인 물리적인 주소로 가리키기 위한 어드레스 테이블이 필요한데 이것을 엠엠유 페이지 테이블(MMU pagetable)이라고 합니다. 이렇게 가상주소가 확보가 되면 개발자는 I-Cache와 D-Cache 사용 유무를 결정할 수가 있어요.

하드웨어 디버거로 MMU Table을 보면 다음과 같아요.

___address_________|_physical___________|_d_|_size____|_permissions_____

C:13D00000--13DFFFFF|A:46200000--462FFFFF| 03| 00100000|P:readwrite U:readwrite

C:13E00000--140FFFFF| | | |

C:14100000--141FFFFF|A:74600000--746FFFFF| 0B| 00100000|P:readwrite U:readwrite

C:14200000--142FFFFF| | | |

C:14300000--14FFFFFF|A:66300000--66FFFFFF| 00| 01000000|P:noaccess U:noaccess

C:15000000--150FFFFF|A:0D000000--0D0FFFFF| 09| 00100000|P:readwrite U:readwrite

C:15100000--151FFFFF|A:00000000--000FFFFF| 00| 00100000|P:noaccess U:noaccess

C:15200000--FFFFFFFF| | | |

친절한 임베디드 시스템 개발자 되기 강좌 글 전체 리스트 (링크) -

친절한 임베디드 시스템 개발자 되기 강좌 글 전체 리스트 (링크) -

댓글